|

|

2-Tages-Seminar und Tutorial: Leiterplatten 7 ...vom CAD-Design zur Baugruppe

Strategien für die Konstruktion eines CAD-Designs. Designregeln für das Placement und das Routing elektronischer Komponenten. Technologien für die Bestückung und die Montage von Baugruppen. Interaktionen zwischen CAD-Design, Leiterplattenfertigung und Baugruppenproduktion

|

Baugruppen

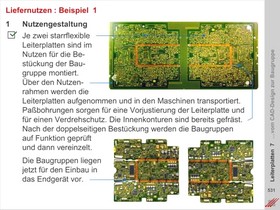

Anwendungen von starren, flexiblen und starrflexiblen Leiterplatten bzw. Baugruppen für diverse Gerätekonzepte. Flexible Leiterplatten als diskrete Übertragungsleitungen und als Quasi-Verbindungskabel für die Geräteverkabelung.

|

Klassifizierung von Baugruppen

Eine Übersicht zu den Strategien für die Montage elektronischer Komponenten auf einer Leiterplatte. Löten, Bonden und Einpressen als prinzipielle Verfahren. Wechselwirkungen zwischen den Basismaterialien, den Lagenaufbauten und der Montagetechnik.

|

|

|

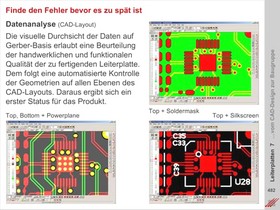

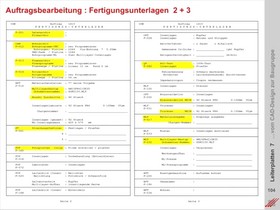

CAM

Anforderungen an die CAM-Bearbeitung von Daten aus dem CAD-Postprozeß. Design-Rule-Check und Prüfung auf Vollständigkeit der Dokumentation. Ergänzung fehlender Informationen und Daten für die fachgerechte Produktion von Leiterplatten.

|

CAD-Bibliothek

Allgemeine Regeln für die Anlage von Bauteilen in der Bibliothek von CAD-Systemen. Routing-Constraints mit Beachtung der Vorgaben für eine problemfreie Bestückung der Baugruppe.

|

|

|

Padstacks

Padstacks als elementare Vorgabe für geometrische Ausprägung von Vias und Lötflächen. "Design for Manufacturing" auf Bibliotheksniveau für ein fertigungsgerechtes und kostenoptimiertes CAD-Layout aus der Perspektive der Elektronikfertigung.

|

Bohrklassen

Erläuterung der unterschiedlichen Bohrklassen und Bohrtypen, die bei der Konstruktion einer Baugruppe eingesetzt werden können. Justagebohrungen für die Montage im Gehäuse, Verdrehschutz für die Bestückung. Varianten für dk- sowie Blind- und Buried Vias.

|

|

|

Logistik

Einblick in die Komplexität des Fertigungsprozesses von Leiterplatten und Baugruppen. Informationen zur Individualität der Produktionsabläufe mit unterschiedlicher technischer Anforderung. Dokumentation von Fertigungsverfahren.

|

Baugruppen

THT- und SMT-Baugruppen. Strategien für die Bestückung. Auswirkungen der Misch- und doppelseitigen Bestückung auf die

langfristige Qualität der Leiterplatte. Bauelementetrends für passive und aktive Bauelemente. Handling und Fehlermechanismen.

|

|

|

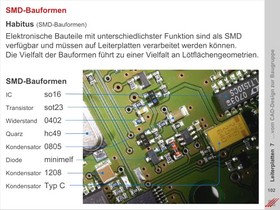

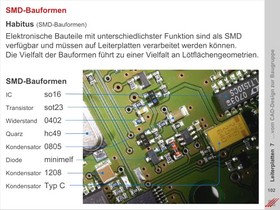

Allgemeine Bauformen

THD und SMD-Komponenten. Gehäuseformen und Abmaße für elektronische und mechanische Bauteile. Standardisierte Grundflächen. Routingempfehlungen. Rastermaße und (Pitch) Pinabstände für alle gängigen Komponenten.

|

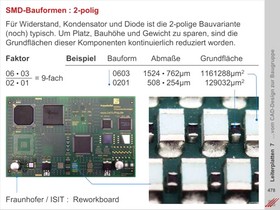

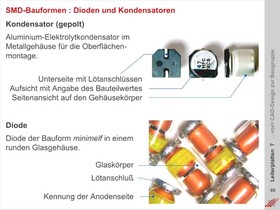

2-polige Bauformen

Quaderförmige Grundformen und Bezeichnungssystematik für 2-polige SMD-Bauelemente. Handling und Logistik von Komponenten.

|

|

|

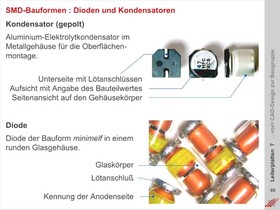

Spezielle Bauformen

Zylinderförmige Bauformen für die senkrechte Montage (Elektrolytkondensatoren) oder für die horizontale Montage (Dioden). Informationen zum Aufbau und zur Fertigung von Bauelementen.

|

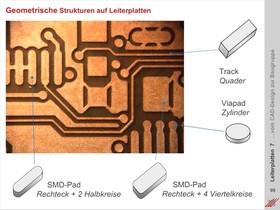

Geometrien

Allgemeine Analysen zur expliziten Berechenbarkeit von Geometrien auf Leiterplatten. Zerlegung des Leiterbildes auf elementare geometrische Grundformen.

|

|

|

Basismaterial

Basismaterialien für starre, flexible und starrflexible ein- und doppelseitige Leiterplatten bis hin zu hochlagigen Multilayern. Eine Übersicht zu diversen Sondermaterialien. Basisinformationen zu Füllstoffen, Harzen und Trägergeweben.

|

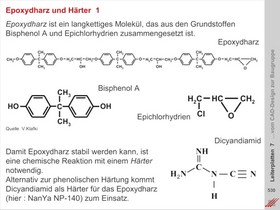

Chemie von Basismaterial

Grundstoffe für die Produktion von FR4-Material. Harzsysteme und Härter. Chemische Substrate für den Aufbau von Basismaterialien. Verarbeitbarkeit von Baugruppen.

|

|

|

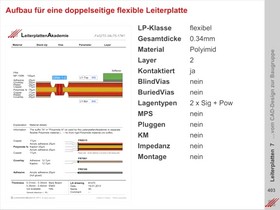

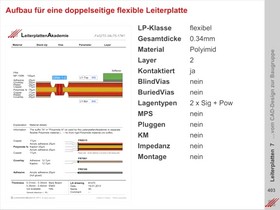

Lagenaufbau

Dokumentation der Basismaterialien und der Aufbaustrategie für ein- und doppelseitige Leiterplatten und Multilayer. Vorgaben für die zuverlässige Produzierbarkeit von Baugruppen.

|

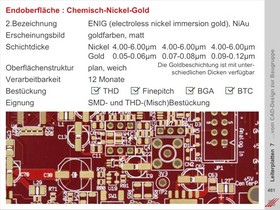

Baugruppenproduktion

Galvanische und Chemische Oberflächen für das Löten elektronischer Baugruppen. Lötmetallurgie, Lötoberflächen, Lötwärmebelastung und -beständigkeit von Leiterplatten und Bauelementen. Prozeßgrenzen, Lötverfahren und Lötprofile (Reflow, Selektiv, Welle). Rework von Baugruppen.

|

|

|

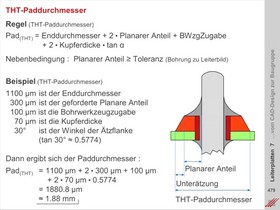

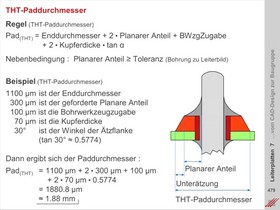

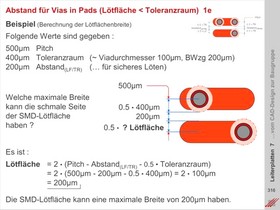

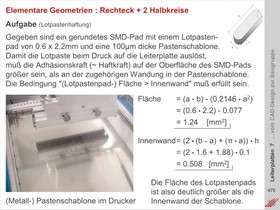

Paddefinitionen

Vorgaben und Regeln für die Geometrie von Lötflächen im Padstack der CAD-Bibliothek. Praktische Berechnung von Restringen für das Löten von THT-Bauteilen auf der Basis der Toleranz-raumbetrachtung.

|

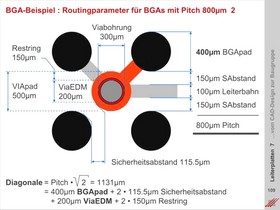

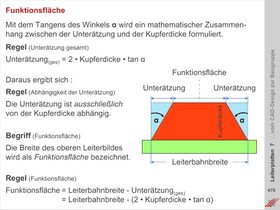

BGA-Pads

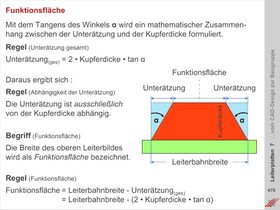

Ermittlung der Funktionsfläche von BGA-Pads unter Berücksichtigung der Funktionsfläche nach dem Unterätzen des Leiterbildes.

Mindestabstände zwischen den Pads von BGAs. Querschnittsgeometrien als Maß für eine Zuverlässigkeitsanalyse.

|

|

|

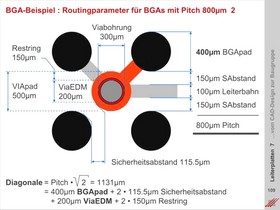

Konstruktionsregeln für BGAs

Allgemeine Designprinzipien. Elementare Geometrien für die Konstruktion der BGA-Padstacks in der Bibliothek des CAD-Systems.

Berechnung von Paddurchmesser, Sicherheitsabstand, Fan-Out-Via, Viadurchmesser und Leiterbahn-breite.

|

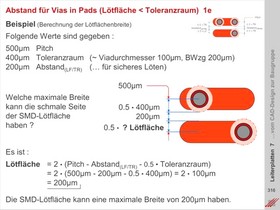

Konstruktionsregeln für VIPs

Kalkulation der Geometrien für ein spezielles Routing im CAD-Layout. Berechnung von Abständen, Vias und Lötflächen für die Routingstrategie mit VIPs (i.e. ViasInPads). Erläuternde Beispielrechnungen und Übungsaufgaben für das Selbststudium.

|

|

|

Funktionsfläche

Die Abhängigkeit der Funktions-fläche vom Produktionsprozeß der Leiterplatte als entscheidende Größe für die verbindliche Vorhersage eines qualitativ hochwertigen Lötprozesses. Die Rückätzung als Maß für die Qualität einer Leiterplatte.

|

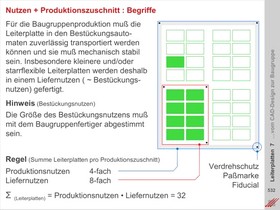

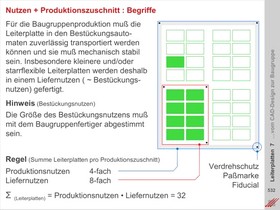

Bestückungsnutzen

Die Nutzengestaltung unter dem Gesichtspunkt einer effektiven und kostenoptimierten Produktion von Leiterplatten und Baugruppen. Empfohlene Nutzenformate. Hinweise zur Ermittlung preiswerter Leiterplattenformate.

|

|

|

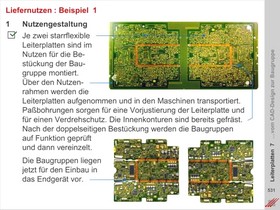

Nutzengestaltung

Geometrische Anforderungen an die Bestückbarkeit von Leiterplattennutzen. Strategien für die Gestaltung von Bestückungsnutzen für starre und starrflexible Leiterplatten respektive Baugruppen.

|

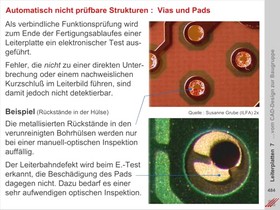

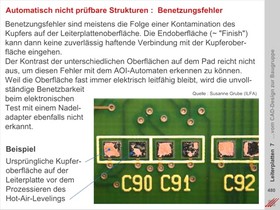

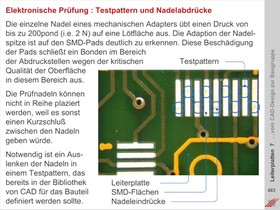

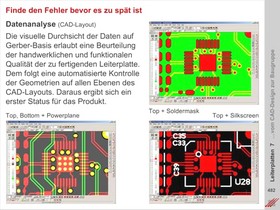

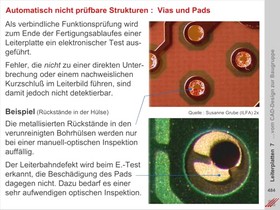

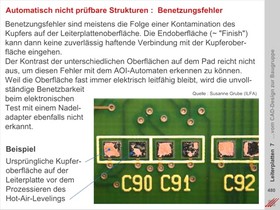

Verifikation

Bewertung der finalen Prüfbarkeit von Leiterplatten. Durch automatische Prüfungen nicht detektierbare Mängel auf Leiterplatten. Der Einfluß qualitativer Fehler auf die langfristige Zuverlässigkeit von Baugruppen.

|

|

|

Verifikation

Analyseverfahren und Untersuchungsmethodik. Bleifreie Lötstellen. Laufende Qualitätskontrollen. AOI-Inspizierbarkeit. Voids.

Verfügbare Prüfmethoden. Grenzen und Möglichkeiten. Bewertung von Fehlerbilder.

|

Designvorgaben

Richtlinien für das CAD-Design. Paßmarken und Lötstopplack. Design for Rework. Empfehlungen für die Anordnung von Bauteilen. Der bestückungsgerechte Einsatz von Durchkontaktierungen. Wärmebelastung und -minimierung durch den Einsatz von Wärmefallen.

|

|

|

Funktionsbewertung

Baugruppen- und Fehlerbewertung. Einstufung der Qualität und Zuverlässigkeit einer elektronischen Baugruppe. Anforderungen an elektronische Geräte. Inspektionskriterien für die Funktion von Leiterplatten und Baugruppen.

|

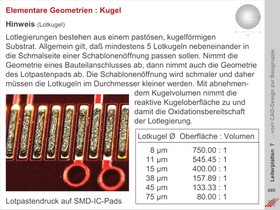

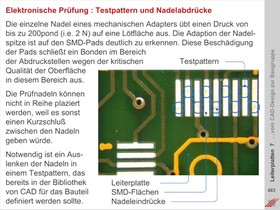

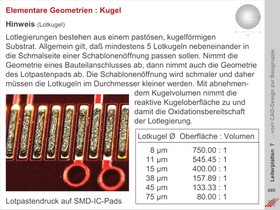

Schablonendruck

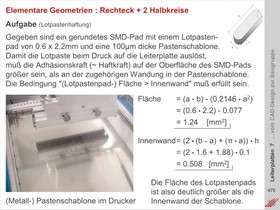

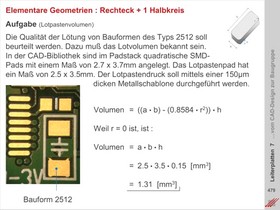

Lotpastenapplikation und Lotpastenvarianten. Lotpasteninspektion. Flußmittel, Auftragsverfahren und Lotpastenschablonen. Druckparameter. Berechnungsmodelle für das Auslösen von Lotpaste. Geometrien im Padstack der CAD-Bibliothek.

|

|

|

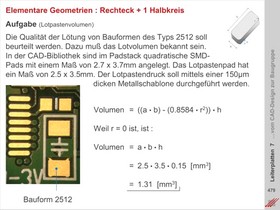

Lotpastenvolumen

Berechnungsmodelle für die aufzubringenden Lotpastenvolumina auf einer Lötfläche. Bewertung der Lötqualität und Vorgaben für eine systematische Beurteilung von Lötprofilen und Lötergebnissen.

|

Lotpastengeometrien

Geeignete technische Lötverfahren für die Bestückung von Finepitch-Bauteilen. Zusammenhänge zwischen den Vorgaben aus der CAD-Bibliothek und der zu wählenden Korngröße für die einzusetzende Lotpaste.

|

|

Wer wird mit dem Seminar/Tutorial "Leiterplatten 7 …vom CAD-Design zur Baugruppe" angesprochen?

Die Möglichkeiten der Leiterplattentechnologie bestimmen die Freiräume bei der Konstruktion von CAD-Layouts und die langfristige zuverlässige Funktion von Baugruppen in Fahrzeugen, Anlagen und Maschinen.

Die Leiterplattentechnologie steht im Zentrum, ist aber verknüpft mit der Konstruktion des CAD-Layouts und der Produktion von Baugruppen.

Durch die Einbindung der Baugruppentechnologie ergibt sich ein gesamtheitlicher Blick auf die Anforderungen an elektronische Baugruppen.

Die Konstrukteure elektronischer Schaltungen und die CAD-Designer und Designerinnen erkennen die Zusammenhänge zwischen der virtuellen CAD-Konstruktion und der Auswirkung auf die reale Produktion und Funktion von elektronischen Geräten. Die Teilnehmer lernen, vor dem Hintergrund gegebener Produktionstoleranzen die Vorgaben für die Routing-Constraints in der CAD-Bibliothek richtig zu hinterlegen.

"Leiterplatten 7 …vom CAD-Design zur Baugruppe" erläutert anschaulich die Leiterplattentechnologie und ihren nachhaltigen Einfluss auf die Konzeptionierung einer Baugruppe.

Sie lernen alle Fertigungsverfahren kennen, die für die Produktion elektronischer Baugruppen erforderlich sind. Die fachgerechte Analyse der Produktdokumentation und der Produktionsdaten erlaubt die verbindliche Einschätzung der Produzierbarkeit eines CAD-Designs.

Sie erlangen eine interdisziplinäre Kompetenz, die Sie in den Stand versetzt, eigenständig über die Konstruktion wirtschaftlich effektiver und vorhersagbar zuverlässiger Elektronikprodukte entscheiden zu können.

Das Seminar ist auch für CAM-Bearbeiter/innen der LP-Hersteller von Bedeutung, weil es die Zusammenhänge zwischen CAD und Leiterplatte erläutert. Es fördert damit auch das partnerschaftliche Miteinander auf der Linie "CAD - CAM - Leiterplatte - Baugruppe".

Die übersichtliche Darstellung der Themen ist ebenso interessant für alle Entscheidungsträger im Bereich Design und Leiterplatte, deren Aufgabe es ist, das Produkt "Baugruppe" führend und beratend zu begleiten.

Ihre Referenten

|

Helge Schimanski, Fraunhofer ISIT

Studium Physikalische Technik an der FH Wedel

Abschluss 1991: Dipl.-Ing (FH) Physikalische Technik

Berufliche Tätigkeiten:

Mai 1991 – April 1998: CEM GmbH

Prozesstechnik (Drucken, Bestücken, Löten elektronischer Baugruppen)

Baugruppen- und Leiterplattenbewertung

Projektleitung bei der Bearbeitung von Entwicklungs- und Untersuchungsdienstleistungen für Industriekunden

|

Seit Mai 1998: Fraunhofer ISIT,

Abteilung Modulintegration mit den Schwerpunkten:

- Leitung des ISIT-Applikationszentrums für innovative Baugruppenfertigung und des ISIT-Rework Centers

- Einwerbung und Projektleitung von öffentlichen Forschungsprojekten

- Einwerbung und Projektleitung von bilateralen Forschungs- und Entwicklungsprojekten für Industriekunden

- Leitung der ISIT-Seminaraktivitäten, Inhouse-Schulungen und praktischen Trainings (Baugruppenfertigung, Prozesstechnik, manuelles Löten, Rework, u.a.)

- Prozessberatung

Mitglied im ZVEI Ad-hoc Arbeitskreis "Repair/Rework", ZVEI Arbeitskreis "Zuverlässigkeit von Leiterplatten" FED-Arbeitskreis "Baugruppe",

"Hamburger Lötzirkel",

VDE/VDI Arbeitskreis "Prüftechniken in der Elektronikproduktion"

|

Arnold Wiemers ist der Leiterplatte seit 1983 verbunden. Von 1985 bis 2009 war er bei der ILFA GmbH in Hannover beschäftigt.

Er war dort verantwortlich für die Fachbereiche CAD und CAM, für die Auftragsvorbereitung und für die technische Dokumentation der Firma ILFA im Internet.

Er arbeitet seit 1982 als freier Softwareentwickler, vornehmlich für branchentypische Applikationen im Bereich der Leiterplatte, wie die Kalkulation und die Fertigungssteuerung von Leiterplatten.

|

Diverse Fachveröffentlichungen. Referent für Seminare, Konferenzvorträge und Workshops zum Thema Leiterplattentechnologie (MFT, MPS, Impedanz, Multilayersysteme, Gerber, Designregeln, LP2010).

Vom IPC zertifizierter CID, CID+ und Instructor. FED-Designer und FED-Referent. Mitarbeit am Schulungskonzept des FED. Mitarbeit in der internationalen "Projektgruppe Design" des FED und des VdL.

Teilnahmegebühren

Präsenz-Seminar: Die Teilnahmegebühr beträgt € 890,- pro Person zzgl. MwSt. Enthalten sind ein Mittagessen sowie Pausengetränke. Jeder Teilnehmer erhält ausführliche Seminarunterlagen und ein Zertifikat.

OnlineSeminar: Die Teilnahmegebühr beträgt € 810,- pro Person zzgl. MwSt. Jeder Teilnehmer erhält ausführliche Seminarunterlagen und ein Zertifikat.

Teilnahmegebühren

Aus organisatorischen Gründen ist die Teilnehmerzahl begrenzt. Anmeldungen werden in der Reihenfolge des Eingangs berücksichtigt. Bitte zahlen Sie erst nach Erhalt der Rechnung. Der Veranstalter behält sich das Recht vor, das Seminar auch nach erfolgter Anmeldebestätigung unter Rückerstattung der Gebühren abzusagen.

Eine schriftliche Stornierung der Anmeldung ist bis eine Woche vor dem Veranstaltungstermin gegen eine Bearbeitungsgebühr in Höhe von 40,00 € möglich, danach ist in jedem Falle der gesamte Betrag fällig. Der Teilnehmer kann den Seminarbesuch jedoch innerhalb eines halben Jahres nach dem Seminartermin nachholen.

|

|

|