|

Seminar und Tutorial

Leiterplatten 54 …LPVerifikation

Strategien, Vorgaben und Möglichkeiten für

die Verifikation von unbestückten Leiterplatten

Halbtags-Tutorial

| Termine: |

Termine für 2020 folgen in Kürze |

|

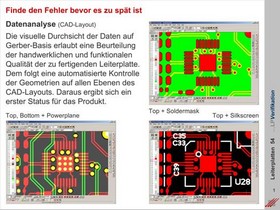

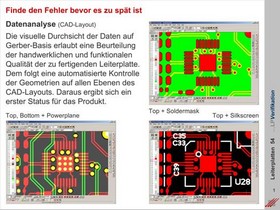

Datenanalyse

Durchsicht der Daten, die der Postprozeß des CAD-Systems an die CAM des Leiterplatten-Herstellers liefert. Prüfung auf Vollständigkeit und fachliche Umsetzbarkeit. Fehlerquellen und Mängel in der Datenübergabe.

|

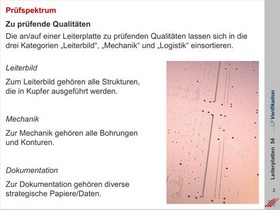

Prüfspektrum

Einordnung der zu prüfenden Qualitäten in ein möglichst komplettes Prüfspektrum für die Verifikation von Leiterplatten. Definition der Wertigkeiten Leiterbild, Mechanik und Dokumentation.

|

|

|

Leiterbilder

Bewertung der Leiterbilder auf einer Leiterplatte für die zuverlässige Produktion der späteren Baugruppe. Ätzfehler und Transportschäden als qualitativer Mangel für die Lötbarkeit einer Leiterplatte. Strategien für die Verifikation von Leiterbildern.

|

Kontaktierung (Dokumentation)

Dokumentation der Bohrstrategie als Voraussetzung für die Produktionsplanung und die systematische Verifikation von Leiterplatten. Interpretation der Begrifflichkeiten zur Dokumentenlenkung und zur Syntax der Produktionsdaten.

|

|

|

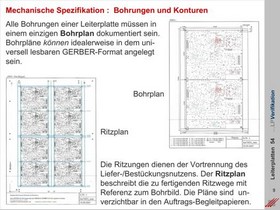

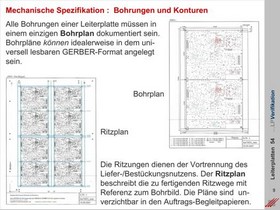

Bohr- und Maßpläne

Beschreibung von Bohrungen und Bohrwerkzeugen für die vergleichende Prüfung von Leiterplatteneigenschaften während der Leiterplatten-Produktion.

Allgemeine Vorgaben für die Maßangaben zu Geometrien von Leiterplatten.

|

AOI

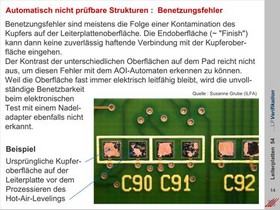

Einsatz der automatisch-optischen Inspektion (AOI) von geometrischen Strukturen auf den Layern von Leiterplatten. Erkennbare und nicht erkennbare Fehlerquellen während der Ausprägung des Leiterbildes.

|

|

|

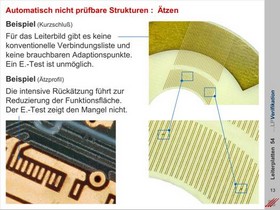

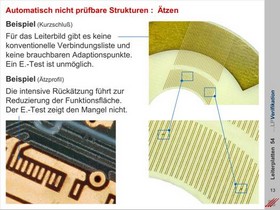

Ätzen

Automatisch nicht prüfbare Leiterbildstrukturen auf Leiterplatten. Elektronisch nicht erkennbare Fehler. Nicht detektierbare Abweichungen vom Leiterbildquerschnitt durch die Rückätzung.

|

Oberfläche

Benetzungsfehler auf der Kupfer-Oberfläche von Leiterplatten. Nur optisch erkennbare Mängel in der Beschichtung. Eingeschränkte elektrische Leitfähigkeit und Lötfähigkeit von Oberflächen.

|

|

|

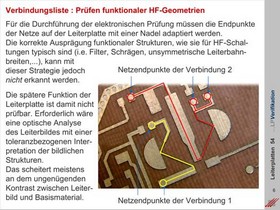

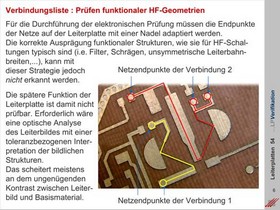

HF-Geometrien

Grundstrategien der elektronischen Prüfung. Optisch nicht vollständig prüfbare Geometrien bei HF-Schaltungen. Adaptierung von Netzpunkten. Datatransfer von Verbindungen. Funktionale Geometrien.

|

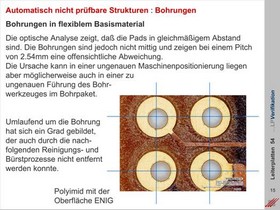

Bohrpositionierung

Passgenauigkeit von Bohrungen zu Leiterbildstrukturen. Gründe für den Versatz zwischen Bild und Mechanik. Allgemein noch akzeptable Toleranzen. Vermessung von Bohrpositionen.

|

|

|

Bohrhülsen

Möglichkeiten der Inspektion der Hülsen von THT-Bohrungen und Vias. Erkennbarkeit von Fehlbelegungen hinsichtlich der Kupferdicke und der galvanischen Oberfläche von Bohrhülsen.

|

Drucke

Analyse der umlaufenden Freistellung von Lötstopdrucken zu SMD-Lötflächen. Prüfung auf korrekt freigestellte Lötflächen. Verifikation von Via-, Carbon- und Abziehlackdrucken auf Leiterplatten. Beurteilung der Qualität von Viadruck und Pluggingverfahren.

|

|

|

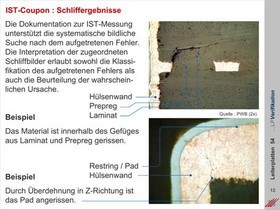

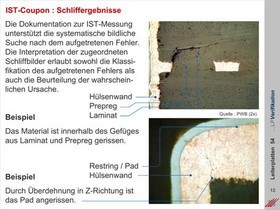

IST-Test

Impedanzmessungen als Mittel für die Qualitätsbeurteilung von Multilayern. Erkennbarkeit von Mikrodelaminationen bei Multilayern durch den IST-Test. Verifikation von Testergebnissen durch die Interpretation von Schliffbildern.

|

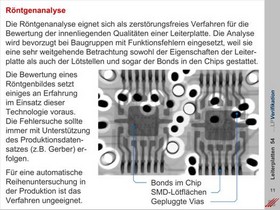

Röntgen

Röntgeninspektion von Multilayern in dreidimensionaler Qualität. Bewertung von Lötflächen, Bonds in Chips und der Kupferdicke von THT-Bohrungen. Vermessen der Paßgenauigkeit der einzelnen Lagen eines Multilayers.

|

|

|

Kantenmetallisierung

Optisch interpretierbare Qualitäten hinsichtlich der Metallisierungen an der Kante von Leiterplatten. Prüfung der Stabilität von Kantenmetallisierungen. Zusammenhang zwischen Endoberfläche und Materialausdehnung.

|

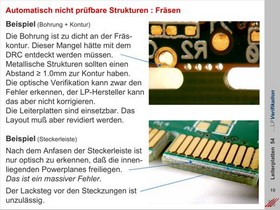

Konturbearbeitung

Automatisch nicht prüfbare Geometrien. Fehlpositionierung von Sollbruchstellen.

Mögliche Kurzschlüsse durch das Anfasen von Steckerleisten. Layoutgeometrien als Fehlerquelle für mechanische Mängel auf Leiterplatten.

|

|

|

Bauteilmontage

Das Einpressen von hochpoligen Steckern und Hochstromkontakten bewerten. Untersuchen der Flächen für das direkte Bonden von ICs auf Leiterplatten.

|

Nutzenstege

Vermessen und bewerten der Positionierung von Nutzenstegen. Diskrete Analyse der Abstände auf starren und starrflexiblen Multilayern in Abhängigkeit von der Geometrie der Leiterplatten. Stegbreiten, Freistellungen und mechanische Stabilität.

|

|

|

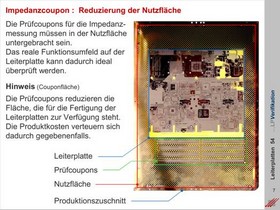

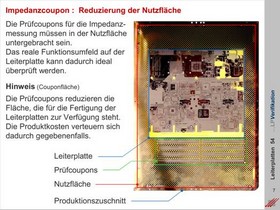

Impedanz

Verfahren für die Messung von Impedanzen und Definition des Meßbereiches. Impedanzcoupons auf Leiterplatten. Impedanzvarianten. Prüfprotokolle.

|

Schliffe

Verifikation mechanischer Eigenschaften von Multilayern über die Interpretation von Schliffbildern. Optionen der Leiterplattenanalyse auf der Basis von Feinschliffen. Kontrolle und Rückannotation zur Fertigung in der Produktion von Leiterplatten und Baugruppen.

|

|

|

Lagenaufbaucoupon

Zerstörungsfreie und delegierbare Prüfung des Aufbaus eines Multilayers mit einem Treppencoupon bzw. eines Treppencoupons. Verifizierung der Lagenreihenfolge, der Lagenabstände und der Kupferdicken in einem Multilayer.

|

Wer wird mit dem Seminar "Leiterplatten 54 …LPVerifikation"

angesprochen?

Das Halbtagsseminar informiert über die Prüfverfahren, die während der

Produktion von Leiterplatten zum Einsatz kommen können.

Zu den offensichtlichen mechanischen Eigenschaften einer Leiterplatte

gehören Längen, Breiten und Dicken sowie die Bohrdurchmesser der

THT-Bohrungen und der Vias. Falls erforderlich, können physikalische

Parameter gemessen werden. Dies betrifft zur Zeit hauptsächlich die Impedanz von Signalleiterbahnen.

Die Analyse von Schliffbilder erlaubt Expertisen zum inneren Aufbau von

Multilayern und zu Schichtdicken in der Hülse.

Die Verifikation der Qualität einer Leiterplatte sichert die Zuverlässigkeit

und die Funktion der elektronischen Baugruppe weitestgehend ab.

Für CAD-Designer/innen sind die nachprüfbaren Eigenschaften einer Leiterplatte eine Leitlinie für die Spezifikation eines Layouts respektive einer Leiterplatte.

"Leiterplatten 54 …LPVerifikation" erläutert die Komplexität und die Aussgagekraft der Tests, die auf einer Leiterplatte zum Einsatz kommen. Üblicherweise sind niemals alle Eigenschaften einer Leiterplatte mit automatischen Systemen prüfbar. In der Praxis gibt es also keine Prüfung, die für sich alle Qualitäten erfassen kann. Es ist stets ein Prüfszenario erforderlich, das die individuellen Eigenschaften einer Leiterplatte möglichst vollständig erfaßt.

Das Seminar ist auch für Mitarbeiter/innen in den Bereichen CAM, Qualitätsmanagement sowie WAK und WEK von Bedeutung, weil es das Verständnis für automatisch prüfbare und nicht prüfbare Anforderungen erläutert. Individuelle Informationen in dynamischen Fertigungsaufträgen können diese Lücken schließen.

Es fördert damit auch das partnerschaftliche Miteinander auf der Linie "CAD - CAM - Leiterplatte - Baugruppe".

Die Darstellung der Themen ist interessant für alle Entscheidungs

träger im Bereich Design und Leiterplatte, deren Aufgabe es ist,

das Produkt "Baugruppe" führend und beratend zu begleiten.

Ihr Referent

|

Arnold Wiemers ist der Leiterplatte seit 1983 verbunden. Von 1985 bis 2009 war er bei der ILFA GmbH in Hannover beschäftigt.

Er war dort verantwortlich für die Fachbereiche CAD und CAM, für die Auftragsvorbereitung und für die technische Dokumentation der Firma ILFA im Internet.

Er arbeitet seit 1982 als freier Softwareentwickler, vornehmlich für branchentypische Applikationen im Bereich der Leiterplatte, wie die Kalkulation und die Fertigungssteuerung von Leiterplatten.

|

Seit 2009 ist er Teilhaber und Technischer Direktor der LeiterplattenAkademie.

Diverse Fachveröffentlichungen. Referent für Seminare, Konferenzvorträge und Workshops zum Thema Leiterplattentechnologie (MFT, MPS, Impedanz, Multilayersysteme, Gerber, Designregeln, LP2010).

Vom IPC zertifizierter CID, CID+ und Instructor. FED-Designer und FED-Referent. Mitarbeit am Schulungskonzept des FED. Mitarbeit in der internationalen "Projektgruppe Design" des FED und des VdL.

Teilnahmegebühren

Die Teilnahmegebühr beträgt € 260,- pro Person zzgl. MwSt. Enthalten sind ausführliche Seminarunterlagen, ein Mittagessen sowie Pausengetränke. Jeder Teilnehmer erhält ein Zertifikat.

Da unsere Online-Anmeldeforlulare jeweils für die Buchung einzelner Seminare ausgelegt sind, empfiehlt sich für eine evtl. Paket-Buchung mehrerer Veranstaltungen eine formlose Anmeldung unter anmeldung@leiterplattenakademie.de

Anmeldebedingungen

Aus organisatorischen Gründen ist die Teilnehmerzahl begrenzt. Anmeldungen werden in der Reihenfolge des Eingangs berücksichtigt. Bitte zahlen Sie erst nach Erhalt der Rechnung. Der Veranstalter behält sich das Recht vor, das Seminar auch nach erfolgter Anmeldebestätigung unter Rückerstattung der Gebühren abzusagen. Nähere Informationen zur Anreise erhalten Sie mit der Rechnung/Anmeldebestätigung.

Eine schriftliche Stornierung der Anmeldung ist bis eine Woche vor dem Veranstaltungstermin gegen eine Bearbeitungsgebühr in Höhe von 40,00 € möglich, danach ist in jedem Falle der gesamte Betrag fällig. Der Teilnehmer kann den Seminarbesuch jedoch innerhalb eines halben Jahres nach dem Seminartermin nachholen.

|